# Monolithic Integration, Performance and Comparison of Self-Aligned and Conventional IGZO Thin-Film Transistors on a Flexible Substrate

Dianne Corsino, Federica Catania, Koichi Ishida, Tilo Meister, Frank Ellinger, Senior Member, IEEE, Giuseppe Cantarella, Member, IEEE, and Niko Münzenrieder, Senior Member, IEEE

Abstract—Flexible electronics, most prominently thinfilm transistors (TFTs) on plastic substrates are considered the prime building block for the realization of innovative wearable systems. Two of the currently most successful fabrication processes of transistors on free standing polymer foils are large-area compatible devices structured by conventional UV lithography and high-speed transistors realized by self-alignment. Here, both processes, based on InGaZnO technology, are combined for the first time. This demonstrates their compatibility, but also showcases the differences between the resulting devices. Concerning the geometry, TFTs with the same nominal designed channel length of  $1.5 \,\mu\mathrm{m}$ , exhibit real channel length of  $1.5 \,\mu\mathrm{m}$  (selfaligned) and  $4.5\,\mu\mathrm{m}$  (conventional). Furthermore, the integrated side by side fabrication enables the electrical comparison of both types of TFTs excluding external factors. While all TFTs exhibit similar threshold voltages around  $0\,\mathrm{V}$  and excellent on/off ratios of  $\approx 10^{10}$ , conventional TFTs are easier to fabricate, and have comparably higher mobilities up to  $16 \,\mathrm{cm^2\,V^{-1}\,s^{-1}}$ . At the same time, self-aligned TFTs demonstrate better AC performance, demonstrating a maximum oscillation frequency of  $216\,\mathrm{MHz}$ . This integration shows new possibilities for the realization of complex systems made from building blocks optimized for reliability and speed.

Index Terms—Flexible electronics, Self-alignment, InGaZnO, Thin-Film Transistors, AC performance

#### I. INTRODUCTION

RLEXIBLE thin-film electronics on large-area plastic substrates have the potential to unobtrusively integrate electronic functionality into everyday objects and hence to connect physical objects to the digital domain [1]. In this context,

Submitted for review xxxxxxx 2022. This work was partially funded by the Autonomous Province of Bozen-Bolzano-South Tyrol's European Regional Development Fund (ERDF) Program: project code EFRE/FESR 1140-PhyLab; in part by the International Joint Cooperation South Tyrol-Switzerland Swiss National Foundation (SNF) FLEXI-BOTS project under Grant 2/34; in part by the Free University of Bozen-Bolzano, via the RTD project FERMI; and in part by the Deutsche Forschungsgemeinschaft (DFG) FFlexCom Initiative, Germany, through the Project WISDOM II under Grant 271795180.

D. Corsino, F. Catania, G. Cantarella, and N. Münzenrieder are with the Free University of Bozen-Bolzano, 39100 Bozen-Bolzano, Italy. (e-mail: niko.muenzenrieder@unibz.it)

K. Ishida, T. Meister, and F. Ellinger, are with the Chair of Circuit Design and Network Theory, TU Dresden, 01069 Dresden, Germany.

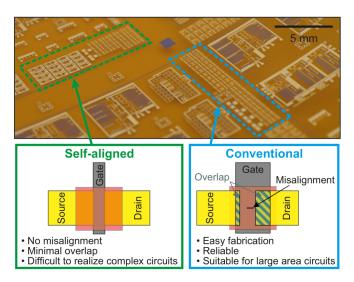

Fig. 1. Integration: Self-aligned and conventional non-self aligned TFTs realized on a single polyimide substrate using an integrated fabrication process.

novel technologies and materials for the fabrication of electronic devices on flexible, but mostly fragile substrates are being developed. Among various types of amorphous and (poly-)crystalline Silicon thin-films, organic semiconductors, carbon nanotubes and different two dimensional materials [2]— [6], oxide semiconductors, in particular amorphous InGaZnO (IGZO) [7], are suitable materials for the realization of thinfilm transistors (TFTs). This is because IGZO provides a good compromise between large area and low temperature fabrication compatibility as well as electrical and mechanical performance. This is reflected by the recent demonstration of complex digital circuits as well as analog systems [8], [9]. Although, the realization of circuits on flexible freestanding large-area substrates which are fast and complex at the same time remains a significant challenge, recent advances resulted in very fast flexible TFTs. Highly scaled flexible InSnO (ITO) and silicon based devices with channel length down to 160 nm exhibited transit frequencies of 2.1 GHz and 3.7 GHz have been reported [10], [11]. However, these are normally fabricated using electron beam lithography, or the transfer of crystalline semiconductor membranes which is not easily scalable and also not compatible with large-area substrates. Other techniques to realize miniaturized TFTs on flexible substrates include focused ion beam milling [12], and two photon laser writing [13], which are also sequential and therefore not easily scalable processes. An alternative process is the fabrication of self-aligned TFTs using e.g. backside illumination. Such processes are regularly employed for oxide based TFTs and resulted in IGZO and ZnO TFTs with transit frequencies ( $f_T$ ) of 1.1 GHz or maximum oscillation frequency of 2.7 GHz, respectively [14], [15]. On a flexible substrate, such a process resulted in flexible IGZO TFTs with a transit frequency  $f_T$  of 135 MHz, and a maximum oscillation frequency  $f_{MAX}$  of 0.4 GHz [16], [17]. By combining this advanced fabrication techniques with conventional fabrication protocols, the advantages of both processes can open up a pathway to more complex, but still fast flexible circuits. As indicated in Fig. 1, this report presents the integration of both conventional and self-aligned TFTs on the same flexible substrate. This not only demonstrates the compatibility of the two technologies, but also allows a direct and absolute fair comparison of the performance of the resulting transistors. The individual features of the two realized types of transistors are described below.

#### A. Conventional TFTs

Conventional TFTs, i.e. transistors entirely fabricated by standard UV lithography, etching and liftoff processes can be fabricated on flexible substrates since decades [18]. Compared to other flexible TFTs, such devices are easy to fabricate, highly reliable, and reproducible, proven by the demonstration of circuits with thousands of TFTs [19]. At the same time, their minimum channel length is particularly limited if conventional TFTs are fabricated on a free standing substrate. Additionally, tolerances are needed to compensate for the expansion and shrinkage of the substrate during the fabrication process. Changes of the substrate size are caused by thermal expansion as well as swelling due to the absorption of liquids. These size variations can reach values of >10 µm on a centimeter sized substrate [16], resulting in misalignment and the need for overlaps between the gate and source-drain metal as shown in Fig. 1-bottom right. This in turn leads to unwanted parasitic capacitances making the realization of fast flexible TFTs by conventional lithography difficult.

# B. Self-aligned TFTs

Flexible TFTs with self-aligned source and drain contacts benefit from the fact that a misalignment of the channel is inherently excluded, and overlaps are minimized. This is because the gate materialization itself acts as mask to structure the TFT channel. This is a significant advantage for the fabrication on flexible substrates, and also eliminates the need for dedicated gate to source/drain overlaps which in turn reduces the parasitic capacitance of the gate. Furthermore, this approach normally simplifies the fabrication of very short TFTs, which makes this technique ideal for high speed devices (illustrated in Fig. 1-bottom left). The shortest flexible TFTs

so far realized with the technique used here exhibit a channel length of  $0.5\,\mu m$  [16]. At the same time, self-aligned TFTs require additional process steps, which can limit the choice of usable materials. e.g. the gate contacts must be resistant against the source drain materialization etching solution. More importantly, self-aligned TFTs require transparent substrates. Unfortunately the transparency of high temperature compatible polymer superstates is often limited. If only partially transparent substrates are used, the uniformity of the self-alignment process can be reduced (mostly due to the absorption of light and the associated heating of the substrate), affecting the reliability of self-aligned TFTs on large areas.

## II. DEVICE MANUFACTURING

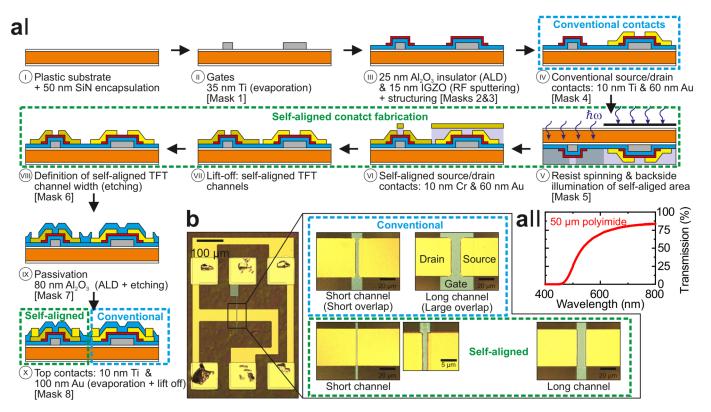

All TFTs were directly fabricated on a free-standing  $7.4\,\mathrm{cm}$   $\times$   $7.4\,\mathrm{cm}$  large polyimide foil using vacuum deposition processes, standard UV lithography and self-aligned lithography. An overview of the fabrication process is given in Fig. 2aI. The maximum temperature employed during the fabrication process was  $150\,^{\circ}\mathrm{C}$ .

# A. Device structure and materials

A bottom-gate inverted staggered and passivated device structure was used to realize all TFTs. The device stack includes Ti gates. This choice of gate material ensures good adhesion to the substrate and resistance against the etching solutions used during the fabrication process.  $SiN_x$  is used as barrier layer, while  $Al_2O_3$  is used as dielectric because it provides a large relative permittivity of  $\approx$ 9.5, and forms a high quality interface with the IGZO semiconductor. Finally, Cr and Ti are used as adhesion layers while Au is utilized for the contacts.

All devices were fabricated on a free-standing  $50\,\mu m$  thick polyimide foil (Kapton E). This material provides a large elastic modulus of  $\approx 5\,\mathrm{GPa}$  [20] and is partially transparent (the measured transmittance is shown in Fig. 2aII). While there are alternative and more transparent polymer foils available for the fabrication of thin-film devices [21]–[23], polyimide is still one of the most common substrates [24]. This is due to its thermal and chemical stability, exhibiting a coefficient of thermal expansion of  $12\times 10^{-6}\,\mathrm{K}^{-1}$ , and a humidity expansion coefficient of  $9\times 10^{-6}\,\mathrm{KRH}^{-1}$  [25].

To make the self-aligned and conventional TFT technologies as comparable as possible, the two types of TFTs were designed with the same dimensions on the lithography masks. Long channel devices with a channel width of 50 µm and a channel length of 10 µm, and short channel devices with a channel width of 50 µm and a channel length of 1.5 µm were fabricated. Here, the channel length of the conventional TFTs is defined by the distance between the source and drain contacts, while for self aligned TFTs the channel length is defined by the length of the gate contact. In addition, conventional TFTs exhibit gate to source/drain overlaps of 15 µm (long channel), and 5 µm (short channel) on the mask. The corresponding high-resolution photo masks were purchased from Computergarphics Jena. The pad layout of the TFTs uses a GSG geometry with a pitch of 150 µm (Fig. 2b). This enables reliable AC characterization through GSG probe tips.

Fig. 2. Fabrication: al) Schematic of the fabrication process flow for the realization of monolithically integrated conventional and self-aligned TFTs on a flexible 50 μm thick polyimide foil. all) Measured transmission spectrum of the polyimide foil used as substrate. b) Micrograph of representative long and short channel TFTs, from the same substrate, fabricated using self-aligned and conventional lithography.

# B. Fabrication

First, the polyimide substrate was cleaned with acetone and isopropanol in an ultrasonic-bath, and then stored in an oven at 200 °C for 24 h. Next, both sides of the substrate were covered with  $50 \,\mathrm{nm}$  thick  $\mathrm{SiN}_x$  using a plasma-enhanced chemical vapor deposition process at 150 °C (Oxford Instruments PECVD 80+). The initial step of the TFT fabrication process itself was the e-beam evaporation of a 35 nm thick Ti bottom gate (Plassys). This layer was structured via lift-off [UV lithography: mask 1]. The gates were insulated by 25 nm thick Al<sub>2</sub>O<sub>3</sub> grown by atomic layer deposition (ALD) at 150 °C using water and trimethylaluminium as precursors (Picosun Sunale R-150B). Next, 15 nm thick IGZO was deposited at room temperature using RF magnetron sputtering, a ceramic target with an atomic composition of In:Ga:Zn:O = 1:1:1:4, and a pure Ar atmosphere (PVD systems). Both the IGZO layer and the Al<sub>2</sub>O<sub>3</sub> layer were structured by wet chemistry, using  $HCl:H_2O = 1:120$ , and  $HNO_3: H_3PO_4: CH_3COOH:$  $H_2O = 1:25:5:5$ , respectively [UV lithography: masks 2+3].

To realize the source and drain contacts on the conventional TFTs,  $10 \,\mathrm{nm}$  of Ti, and  $60 \,\mathrm{nm}$  Au were e-beam evaporated (Plassys), and structured by lift-off [UV lithography: mask 4].

The realization of self-aligned source and drain contacts started with the deposition of positive AZ 4533 photoresist. The areas of the substrate carrying self-aligned TFTs were then illuminated through the backside of the partially transparent substrate using the opaque Ti gates as mask. This was done using a LOT Oriel Hg UV lamp at 400 W. The optical power

transmitted through the polyimide substrate (measured at a wavelength of  $400 \,\mathrm{nm}$ ) is  $0.04 \,\mathrm{mW \, cm^{-2}}$ . To account for this, the total exposure time was 16 min. Here, a metallic mask [masks 5] was used to shield the conventional TFTs. An additional conventional lithography can be used to illuminate the photoresist on top of the gate contact pads of selfaligned transistors [UV lithography: mask 5a]. This step was performed to demonstrate its feasibility, but is not relevant for the fabrication of individual devices, however, it is essential if circuits should be realized. The resist was developed for 225 s using AZ developer. This development time removed virtually all exposed resists. At the same time, it also determines the final gate to source/drain overlaps due to the unavoidable over-development of the positive photo-resists. After the resist development, a line of photo resist was perfectly aligned to each gate. To form the TFT channels, 10 nm of Cr and 60 nm of Au were e-beam evaporated (Plassys) and structured by liftoff using the self-aligned resist. Finally, the channel width and the contact pads of the self-aligned transistors were defined by wet etching using  $50 \text{ g} \text{ (NH}_4)_2\text{Ce(NO}_3)_6 + 12 \text{ g} \text{ CH}_3\text{COOH} +$  $250 \,\mathrm{mL}$  H<sub>2</sub>O and  $15 \,\mathrm{g}$  KI +  $5 \,\mathrm{g}$  I +  $100 \,\mathrm{mL}$  H<sub>2</sub>O to etch the Cr and Au, respectively [UV lithography: mask 6].

Subsequently, all devices on the substrate were passivated with a structured  $80\,\mathrm{nm}$  thick  $\mathrm{Al_2O_3}$  layer, similar to the gate insulator layer [UV lithography: mask 7]. Lastly, the fabrication process was concluded by the deposition of additional contact pads made from  $10\,\mathrm{nm}$  Ti (e-beam, MBRAUN EB M-4 ) and  $100\,\mathrm{nm}$  Au (thermal, MBRAUN Evaporator ECOVap and ProVap - TP700), and structured by lift-off [UV

lithography: mask 8].

#### III. RESULTS AND DISCUSSION

The fabricated TFTs were characterized for their AC and DC performance. All measurements were carried out at room temperature under standard lab conditions. All performance parameters were extracted from TFTs in the saturation regime. Finally, to guarantee comparability, the same bias voltages were used for self-aligned and conventional TFTs.

This report focuses on the electrical performance of the fabricated TFTs. At the same time, it is worth mentioning that for flexible TFTs, the mechanical properties are also of paramount importance. However, the influence of bending on the AC and DC performance of conventional and self-aligned TFTs has been investigated in detail by our group in the past [16], [26]. There is no indication that the integration of both types of TFTs has any influence on their flexibility.

# A. Geometry

A fully fabricated TFT is shown in Fig. 2b. While conventional and self-aligned, long and short channel TFTs exhibit the same dimensions on the photo masks, the micrographs show that the different source/drain fabrication techniques result in noticeably different measured channel dimensions. The channel width is increased in both cases: +4 µm (conventional), and +1 µm (self-aligned). The channel length is as designed for short channel self-aligned TFTs, and slightly increased for long channel self-aligned TFTs. At the same time, the channel length is significantly increased by values up to +3.5 µm for the conventional TFTs. These differences reflect the fact that the width and length of the different TFT channels are structured using different technologies (conventional liftoff, self-alignment, and etching). An overview of all TFT dimensions is given in Fig. 3a. Finally, the self aligned process results in measured short and consistent gate to source/drain overlaps of 0.8 µm.

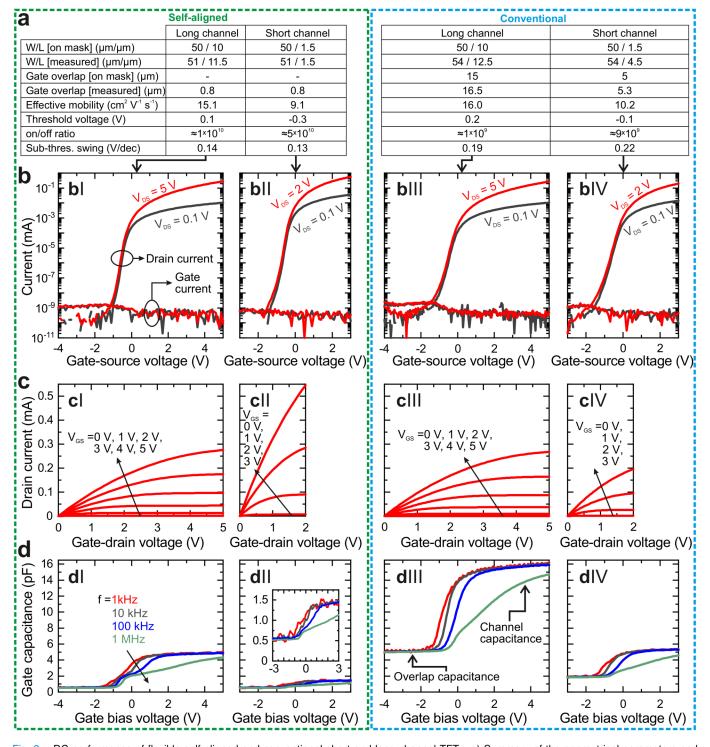

## B. DC performance & Capacitance

The DC characterization of TFTs, consisting in both voltage-current curves and capacitance-voltage curve, were performed with a Keysight B1500A parameter analyzer. The standard DC performance parameters were extracted using the Shichman-Hodges model [27] and the actual measured TFT dimensions. All TFTs were characterized in the linear and saturation regime. However, the bias voltages had to be limited when measuring the short channel TFTs to avoid a breakdown of the channel ( $V_{GS}$ <3 V,  $V_{DS}$ <2 V). This made it impossible to drive short channel TFTs into full current saturation for all  $V_{GS}$  values >1 V (Figs. 3cII and 3cIV). The TFT transfer and output characteristics are shown in Figs. 3b and 3c. The measurements show low gate leakage current and outstanding on/off current ratios around  $10^{10}$ . The DC performance parameters extracted from the saturation regime are threshold voltage, effective carrier mobility, and sub-threshold swing (inverse of sub-threshold slope) as summarized in Fig. 3a. The reported values are in line with

state-of-the-art flexible IGZO TFTs [24]. The most notable difference between the different TFTs concerns the effective mobility. While the intrinsic IGZO carrier mobility is the same for all devices, the effective mobility is influenced by the contact resistance. The contact resistances of these TFTs at the same time decrease with increasing gate-source voltage, and with increasing gate to source/drain overlaps (see [28] for more details). Furthermore, the contact resistance is more relevant for short channel TFTs with low channel resistance. Consequently, conventional TFTs (with larger overlap), and short channel TFTs exhibit larger effective mobilities than their corresponding counterparts. This leads to measured variations between  $9.1\,\mathrm{cm}^2\,\mathrm{V}^{-1}\,\mathrm{s}^{-1}$  and  $16\,\mathrm{cm}^2\,\mathrm{V}^{-1}\,\mathrm{s}^{-1}$ . The different channel dimensions, effective mobilities and bias voltages also lead to different maximum transconductance values for long channel 0.12 mS (conventional), 0.11 mS (self-aligned), and short channel 0.21 mS (conventional), 0.52 mS (self-aligned) transistors.

The measured gate to source/drain capacitances of the TFTs are shown in Figs. 3d. These measurements were performed for different frequencies between 1 kHz and 1 MHz while the source and drain contacts were externally connected. For low gate bias voltages (TFT off), the measurements show the parasitic overlap capacitance, which reached values of 0.3 pF, 2 pF, and 5.2 pF for TFTs with overlaps of 0.8 μm, 5.3 μm, and 16.5 µm, respectively. For positive gate bias voltages (TFT on), the measurements include both the parasitic overlap capacitance and the capacitance of the channel. The values depend on the frequency as trap states in the channel cannot be occupied and deoccupied at high frequencies [29]. The extracted total gate capacitances for long channel TFTs are 16.1 pF (conventional) and 4.8 pF (self-aligned), while they are only 5.3 pF (conventional) and 1.45 pF (self-aligned) for short channel transistors. These values correspond well with the geometry of the TFTs (notice that the semiconductor island is wider than the channel width, and that the overlaps are different for the conventional long channel, the conventional short channel, and the self-aligned TFTs).

# C. AC performance

First the AC performance of the TFTs can be estimated by calculating the transit frequency  $f_T$  according equation 1 [30]:

$$f_t = \frac{g_m}{2\pi C_G} \tag{1}$$

here  $g_m$  is the transconductance and  $C_G$  is the gate capacitance. Both values are known from the DC characterization. Utilizing Eq 1,  $f_T$  is calculated to be 1.1 MHz (conventional), and 3.7 MHz (self-aligned) for long channel transistors, and 6.2 MHz (conventional), and 56.9 MHz (self-aligned) for short channel transistors. Here, it is worth mentioning that conventional as well as self-aligned flexible IGZO TFTs can reach higher  $f_T$  if the bias voltages and dimensions are individually optimized [24]. However, this would limit the comparability of the devices and is not pursued here.

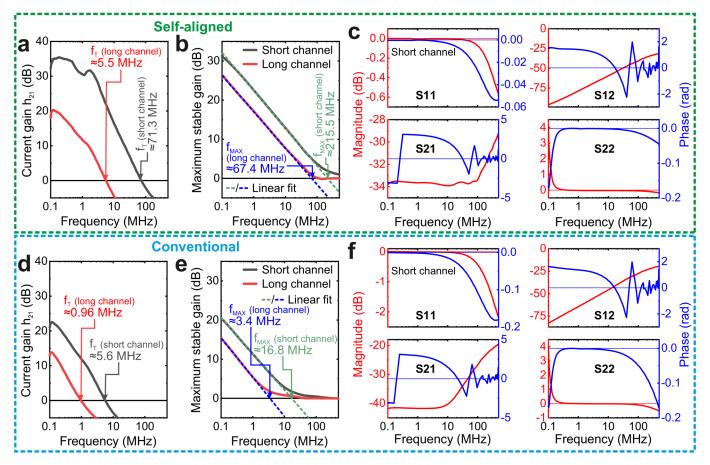

The direct measurement of the AC performance (Fig. 4) was performed by acquiring the scattering parameters of the

Fig. 3. DC performance of flexible self aligned and conventional short and long channel TFTs. a) Summary of the geometrical parameters and the DC performance of various TFTs. b) Transfer characteristics (incl. gate leakage current) measured in the linear and the saturation regime. c) Measured output characteristics. d) Measured gate capacitance (extracted for different measurement frequencies while the source and drain contacts were connected).

TFTs using a Keysight E5061B ENA vector network analyzer and GSG probe tips. Here, DC bias voltages to one channel were applied by the network analyzer (port 1), while a DC bias to port 2 was applied utilizing an external bias-T and a Keysight SMU. Prior to any measurement, the system was calibrated using an open, short and  $50\,\Omega$  load. During the measurements, the source was grounded, while port 1 and

port 2 were connected to the gate and the drain of the TFTs. All measurements were performed at frequencies between 100 kHz and 500 MHz. Examples of the resulting scattering parameters for a self-aligned and a conventional TFT (measured at the same bias voltages of  $V_{GS}=V_{DS}=2\,V$ ) are shown in Figs. 4c and 4f. The S-parameters were then used to calculate the current gain  $h_{21}$  (Figs. 4a and 4d) [31]. Next,  $f_T$

Fig. 4. TFT AC performance: a) Measured current gain, and resulting transit frequency of a long and a short channel self-aligned TFT. b) Measured maximum stable gain, and resulting maximum oscillation frequency of a long and a short channel self-aligned TFT. c) Representative s-parameters of a short channel self-aligned TFT used to determine the frequency performance. d) Measured current gain, and resulting transit frequency of a long and a short channel conventional TFT. e) Measured maximum stable gain, and resulting maximum oscillation frequency of a long and a short channel conventional TFT. f) Representative s-parameters of a short channel conventional TFT used to determine the frequency performance. The DC bias points were:  $V_{GS}=3$  V,  $V_{DS}=5$  V (long channel TFTs), and  $V_{GS}=V_{DS}=2$  V (short channel TFTs).

was extracted as the unity gain frequency of the current gain. The experimental values for  $f_T$  are  $0.96\,\mathrm{MHz}$  (conventional), and 5.5 MHz (self-aligned) for long channel transistors, and 5.6 MHz (conventional), and 71.3 MHz (self-aligned) for short channel transistors. These values are generally in very good agreement with the calculation. The only difference is observed for the short channel self-aligned TFT, this is due to an overestimation of the gate capacitance which could only be measured at frequencies <1 MHz. Finally, the S-parameters were also used to calculate the maximum stable gain (Figs. 4b and 4e) of the transistors [17]. It is used to determine the maximum oscillation frequency  $f_{MAX}$  of the TFTs.  $f_{MAX}$  is the frequency at which a power gain of unity can be reached, it is traditionally larger than  $f_T$ . The  $f_{MAX}$  extracted here are: 3.4 MHz (conventional), and 67.4 MHz (self-aligned) for long channel transistors, and 16.8 MHz (conventional), and 215.5 MHz (self-aligned) for short channel transistors, which are in line with the expectations.

# IV. CONCLUSION

A new integrated fabrication process for the realization of conventional and self-aligned IGZO TFTs on a flexible polymer foil was investigated and demonstrated. The full process

utilizes nine lithography masks plus self-aligned lithography based on backside illumination through the substrate. Long and short channel TFTs were fabricated to demonstrate the possibility of realizing TFTs with bespoke performance. The resulting substrate includes reliable conventional TFTs with effective mobilities up to  $16 \,\mathrm{cm}^2 \,\mathrm{V}^{-1} \,\mathrm{s}^{-1}$ , and self-aligned TFTs with a maximum oscillation frequency up to 216 MHz, while the TFT gate capacitance can be tuned by more than one order of magnitude. Both types of TFTs were fabricated using the same metallic, insulating, and semiconducting thinfilms deposited on a single flexible substrate. This integrated fabrication allows the direct comparison of the TFTs electrical DC and AC performance confirming the trends observed for similar TFTs fabricated on different substrates in the past. In the context of analog integrated circuits, which are particularly influenced by the performance of individual TFTs, it is suggested that self-aligned TFTs are used for high-speed circuits, while the higher reliability and effective mobility of conventional TFTs make them ideal building blocks for current mirrors or low-frequency, high-gain amplifiers. Finally, although designed with the nominally same channel dimensions on the lithography mask, the different source/drain manufacturing techniques of conventional and self-aligned TFTs result in significantly different final channel lengths on the substrate. This has to be considered when designing future integrated circuits based on conventional and self-aligned flexible TFTs.

#### REFERENCES

- [1] A. Nathan, A. Ahnood, M. T. Cole, S. Lee, Y. Suzuki, P. Hiralal, F. Bonaccorso, T. Hasan, L. Garcia-Gancedo, A. Dyadyusha et al., "Flexible electronics: the next ubiquitous platform," Proceedings of the IEEE, vol. 100, no. Special Centennial Issue, pp. 1486–1517, 2012. [Online]. Available: 10.1109/JPROC.2012.2190168

- [2] T.-K. Nguyen, S. Yadav, T.-A. Truong, M. Han, M. Barton, M. Leitch, P. Guzman, T. Dinh, A. Ashok, H. Vu *et al.*, "Integrated, transparent silicon carbide electronics and sensors for radio frequency biomedical therapy," *ACS nano*, vol. 16, no. 7, pp. 10890–10903, 2022. [Online]. Available: 10.1021/acsnano.2c03188

- [3] K. Liu, B. Ouyang, X. Guo, Y. Guo, and Y. Liu, "Advances in flexible organic field-effect transistors and their applications for flexible electronics," *npj Flexible Electronics*, vol. 6, no. 1, pp. 1–19, 2022. [Online]. Available: 10.1038/s41528-022-00133-3

- [4] D. Akinwande, N. Petrone, and J. Hone, "Two-dimensional flexible nanoelectronics," *Nature communications*, vol. 5, no. 1, pp. 1–12, 2014. [Online]. Available: 10.1038/ncomms6678

- [5] S. Park, M. Vosguerichian, and Z. Bao, "A review of fabrication and applications of carbon nanotube film-based flexible electronics," *Nanoscale*, vol. 5, no. 5, pp. 1727–1752, 2013. [Online]. Available: 10.1039/C3NR33560G

- [6] A. Ahmed, S. Sharma, B. Adak, M. M. Hossain, A. M. LaChance, S. Mukhopadhyay, and L. Sun, "Two-dimensional mxenes: New frontier of wearable and flexible electronics," *InfoMat*, vol. 4, no. 4, p. e12295, 2022. [Online]. Available: 10.1002/inf2.12295

- [7] K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, "Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors," *Nature*, vol. 432, no. 7016, pp. 488–492, 2004. [Online]. Available: 10.1038/nature03090

- [8] J. Biggs, J. Myers, J. Kufel, E. Ozer, S. Craske, A. Sou, C. Ramsdale, K. Williamson, R. Price, and S. White, "A natively flexible 32-bit Arm microprocessor," *Nature*, vol. 595, no. 7868, pp. 532–536, 2021. [Online]. Available: 10.1038/s41586-021-03625-w

- [9] T. Meister, K. Ishida, C. Carta, N. Münzenrieder, and F. Ellinger, "Flexible electronics for wireless communication: A technology and circuit design review with an application example," *IEEE Microwave Magazine*, vol. 23, no. 4, pp. 24–44, 2022. [Online]. Available: 10.1109/MMM.2021.3136684

- [10] M. Wang, M. Tian, Z. Zhang, S. Li, R. Wang, C. Gu, X. Shan, X. Xiong, X. Li, R. Huang et al., "High performance gigahertz flexible radio frequency transistors with extreme bending conditions," in 2019 IEEE International Electron Devices Meeting (IEDM). IEEE, 2019, pp. 8–2. [Online]. Available: 10.1109/IEDM19573.2019.8993531

- [11] G. Qin, J.-H. Seo, Y. Zhang, H. Zhou, W. Zhou, Y. Wang, J. Ma, and Z. Ma, "Rf characterization of gigahertz flexible silicon thin-film transistor on plastic substrates under bending conditions," *IEEE electron device letters*, vol. 34, no. 2, pp. 262–264, 2013. [Online]. Available: 10.1109/LED.2012.2231853

- [12] N. Münzenrieder, I. Shorubalko, L. Petti, G. Cantarella, B. Shkodra, T. Meister, K. Ishida, C. Carta, F. Ellinger, and G. Tröster, "Focused ion beam milling for the fabrication of 160 nm channel length IGZO TFTs on flexible polymer substrates," *Flexible and Printed Electronics*, vol. 5, no. 1, p. 015007, 2020. [Online]. Available: 10.1088/2058-8585/ab639f

- [13] L. Petti, E. Greco, G. Cantarella, N. Münzenrieder, C. Vogt, and G. Tröster, "Flexible In-Ga-Zn-O thin-film transistors with sub-300-nm channel lengths defined by two-photon direct laser writing," *IEEE Transactions on Electron Devices*, vol. 65, no. 9, pp. 3796–3802, 2018. [Online]. Available: 10.1109/TED.2018.2851926

- [14] C. Tückmantel, U. Kalita, T. Haeger, M. Theisen, U. Pfeiffer, and T. Riedl, "Amorphous indium-gallium-zinc-oxide TFTs patterned by self-aligned photolithography overcoming the ghz threshold," *IEEE Electron Device Letters*, vol. 41, no. 12, pp. 1786–1789, 2020. [Online]. Available: 10.1109/LED.2020.3029956

- [15] Y. Mehlman, C. Wu, S. Wagner, N. Verma, and J. C. Sturm, "Gigahertz zinc-oxide TFT-based oscillators," in 2019 Device Research Conference (DRC). IEEE, 2019, pp. 63–64. [Online]. Available: 10.1109/DRC46940.2019.9046405

- [16] N. Münzenrieder, L. Petti, C. Zysset, T. Kinkeldei, G. A. Salvatore, and G. Tröster, "Flexible self-aligned amorphous InGaZnO thin-film transistors with submicrometer channel length and a transit frequency of 135 MHz," *IEEE Transactions on Electron Devices*, vol. 60, no. 9, pp. 2815–2820, 2013. [Online]. Available: 10.1109/TED.2013.2274575

- [17] N. Münzenrieder, K. Ishida, T. Meister, G. Cantarella, L. Petti, C. Carta, F. Ellinger, and G. Tröster, "Flexible InGaZnO TFTs with fmax above 300 MHz," *IEEE Electron Device Letters*, vol. 39, no. 9, pp. 1310–1313, 2018. [Online]. Available: https://doi.org/10.1109/LED.2018.2854362

- [18] T. P. Brody, "The thin film transistor—a late flowering bloom," *IEEE Transactions on Electron Devices*, vol. 31, no. 11, pp. 1614–1628, 1984. [Online]. Available: 10.1109/T-ED.1984.21762

- [19] K. Myny, "The development of flexible integrated circuits based on thin-film transistors," *Nature electronics*, vol. 1, no. 1, pp. 30–39, 2018. [Online]. Available: 10.1038/s41928-017-0008-6

- [20] H. Gleskovas, S. Wagner, and Z. Suo, "Rugged a-Si: H TFTs on plastic substrates," MRS Online Proceedings Library, vol. 557, no. 1, pp. 653–658, 1999. [Online]. Available: 10.1557/PROC-557-653

- [21] H. Zuo, G. Qian, H.-B. Li, F. Gan, Y. Fang, X. Li, J. Dong, X. Zhao, and Q. Zhang, "Reduced coefficient of linear thermal expansion for colorless and transparent polyimide by introducing rigid-rod amide units: synthesis and properties," *Polymer Chemistry*, vol. 13, pp. 2999–3008, 2022. [Online]. Available: 10.1039/D2PY00062H

- [22] J. A. Spechler, T.-W. Koh, J. T. Herb, B. P. Rand, and C. B. Arnold, "A transparent, smooth, thermally robust, conductive polyimide for flexible electronics," *Advanced Functional Materials*, vol. 25, no. 48, pp. 7428–7434, 2015. [Online]. Available: 10.1002/adfm.201503342

- [23] F. Catania, H. De Souza Oliveira, P. Lugoda, G. Cantarella, and N. Münzenrieder, "Thin-film electronics on active substrates: review of materials, technologies and applications," *J. Phys. D: Appl. Phys.*, Apr. 2022. [Online]. Available: 10.1088/1361-6463/ac6af4

- [24] G. Cantarella, J. Costa, T. Meister, K. Ishida, C. Carta, F. Ellinger, P. Lugli, N. Münzenrieder, and L. Petti, "Review of recent trends in flexible metal oxide thin-film transistors for analog applications," *Flexible Printed Electron.*, vol. 5, no. 3, p. 033001, Aug. 2020. [Online]. Available: 10.1088/2058-8585/aba79a

- [25] C. Forbes, A. Gelbman, C. Turner, H. Gleskova, and S. Wagner, "A rugged conformable backplane fabricated with an a-Si: H TFT array on a polyimide substrate," in *SID Symposium Digest of Technical Papers*, vol. 33, no. 1. Wiley Online Library, 2002, pp. 1200–1203. [Online]. Available: 10.1889/1.1830161

- [26] N. Münzenrieder, L. Petti, C. Zysset, G. A. Salvatore, T. Kinkeldei, C. Perumal, C. Carta, F. Ellinger, and G. Tröster, "Flexible a-IGZO TFT amplifier fabricated on a free standing polyimide foil operating at 1.2 MHz while bent to a radius of 5 mm," in 2012 International Electron Devices Meeting. IEEE, 2012, pp. 5–2. [Online]. Available: 10.1109/IEDM.2012.6478982

- [27] H. Shichman and D. A. Hodges, "Modeling and simulation of insulated-gate field-effect transistor switching circuits," *IEEE Journal* of Solid-State Circuits, vol. 3, no. 3, pp. 285–289, 1968. [Online]. Available: http://doi.org/10.1109/JSSC.1968.1049902

- [28] N. Münzenrieder, G. A. Salvatore, L. Petti, C. Zysset, L. Büthe, C. Vogt, G. Cantarella, and G. Tröster, "Contact resistance and overlapping capacitance in flexible sub-micron long oxide thin-film transistors for above 100 MHz operation," *Applied Physics Letters*, vol. 105, no. 26, p. 263504, 2014. [Online]. Available: https://doi.org/10.1063/1.4905015

- [29] M. D. Jacunski, M. S. Shur, and M. Hack, "Threshold voltage, field effect mobility, and gate-to-channel capacitance in polysilicon TFTs," *IEEE Transactions on Electron Devices*, vol. 43, no. 9, pp. 1433–1440, 1996. [Online]. Available: 10.1109/16.535329

- [30] U. Zschieschang, J. W. Borchert, M. Giorgio, M. Caironi, F. Letzkus, J. N. Burghartz, U. Waizmann, J. Weis, S. Ludwigs, and H. Klauk, "Roadmap to gigahertz organic transistors," *Advanced Functional Materials*, vol. 30, no. 20, p. 1903812, 2020. [Online]. Available: 10.1002/adfm.201903812

- [31] D. Lovelace, J. Costa, and N. Camilleri, "Extracting small-signal model parameters of silicon MOSFET transistors," in 1994 IEEE MTT-S International Microwave Symposium Digest (Cat. No. 94CH3389-4). IEEE, 1994, pp. 865–868. [Online]. Available: 10.1109/MWSYM.1994.335220